Auto identification method for redundant switches in converters based on graph theory

-

摘要:

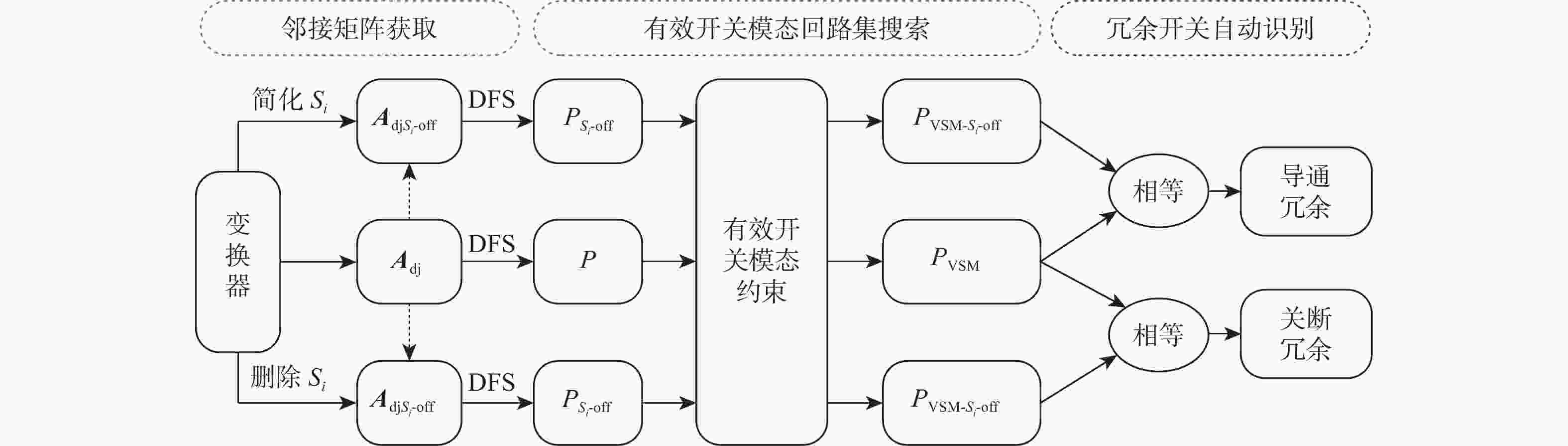

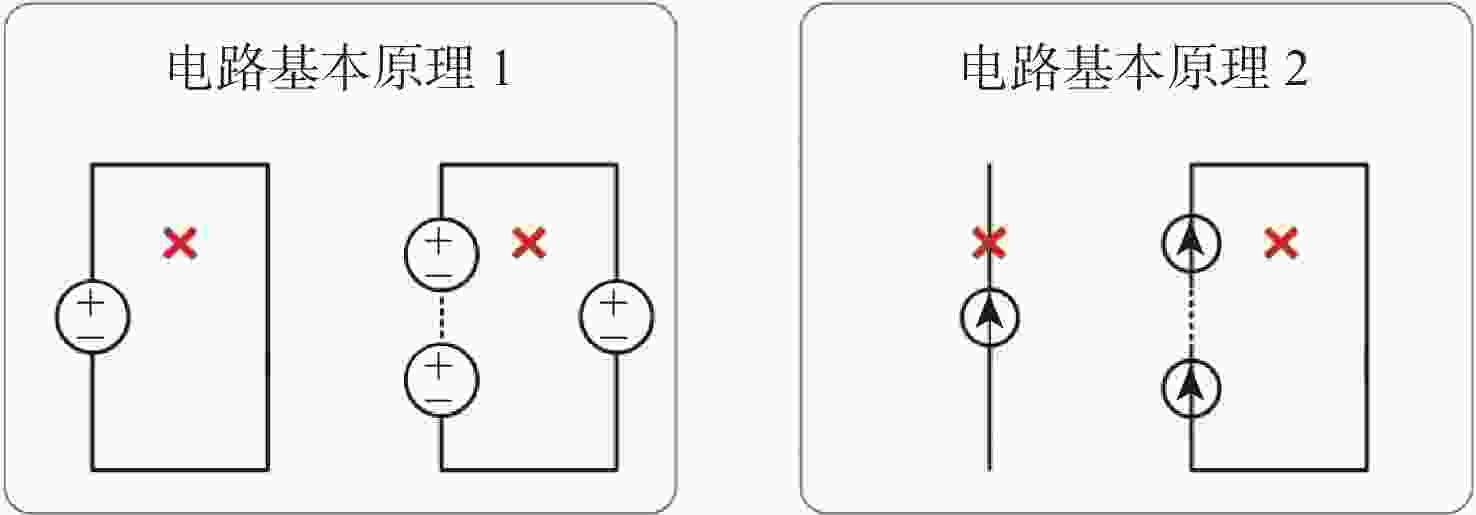

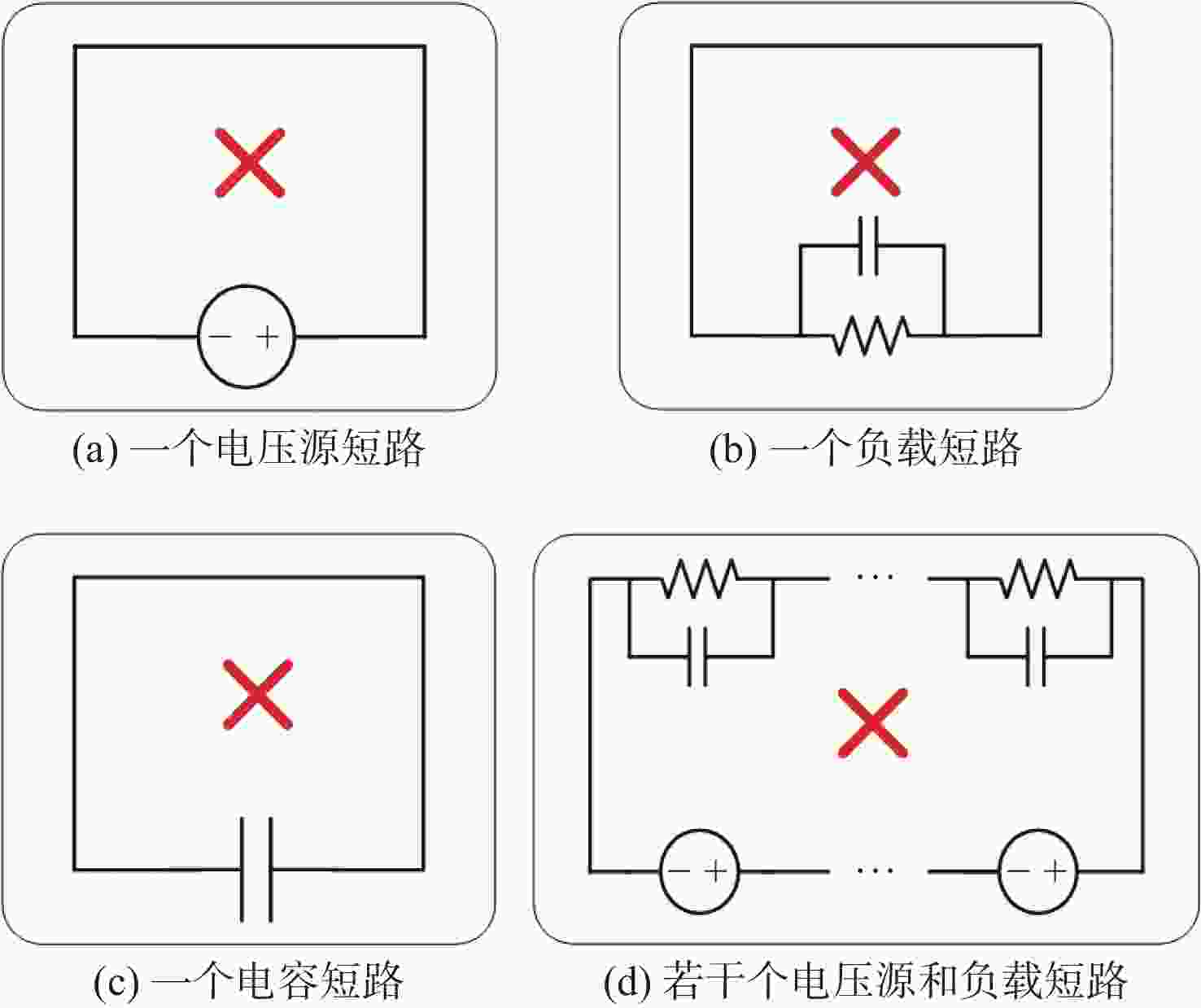

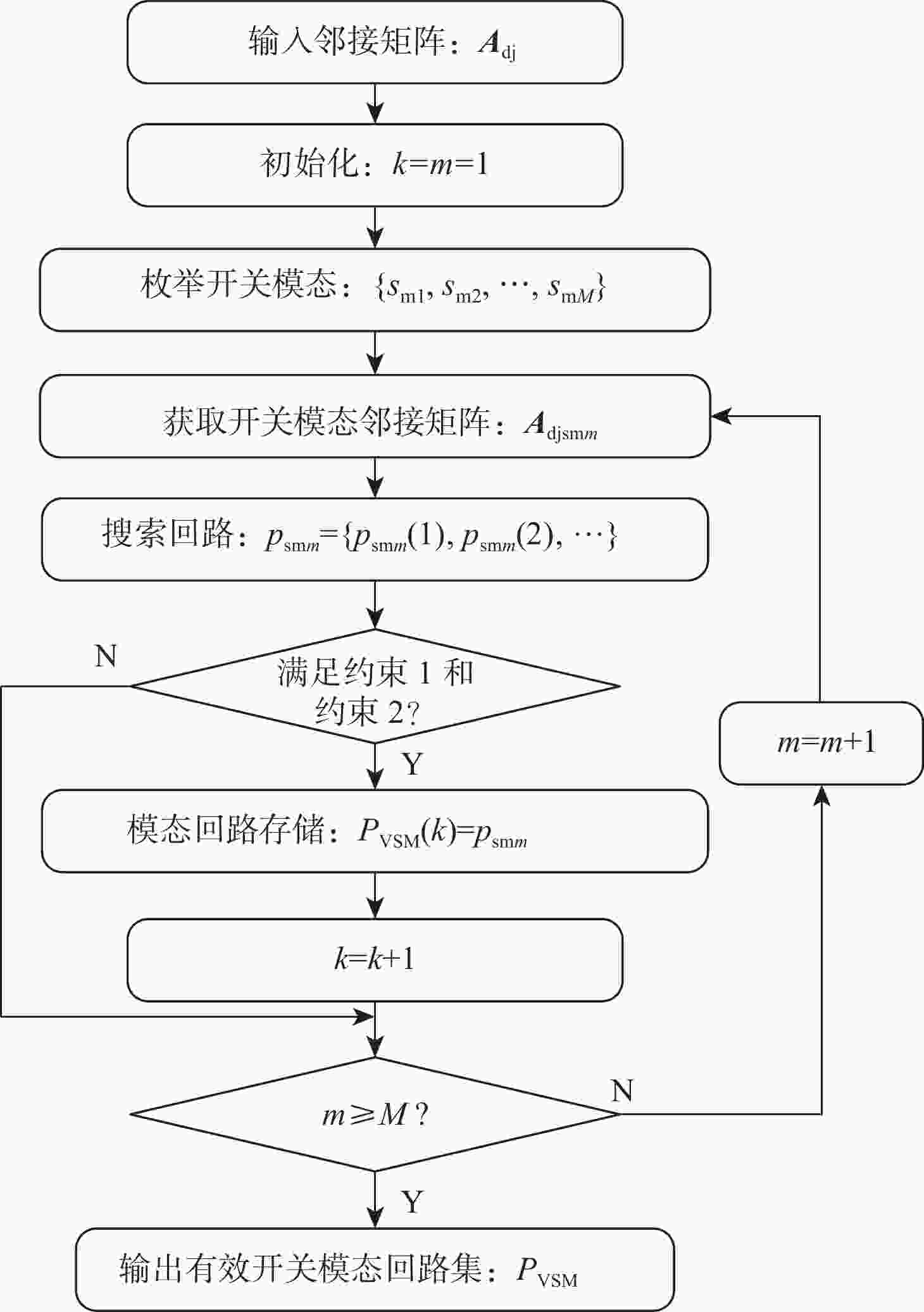

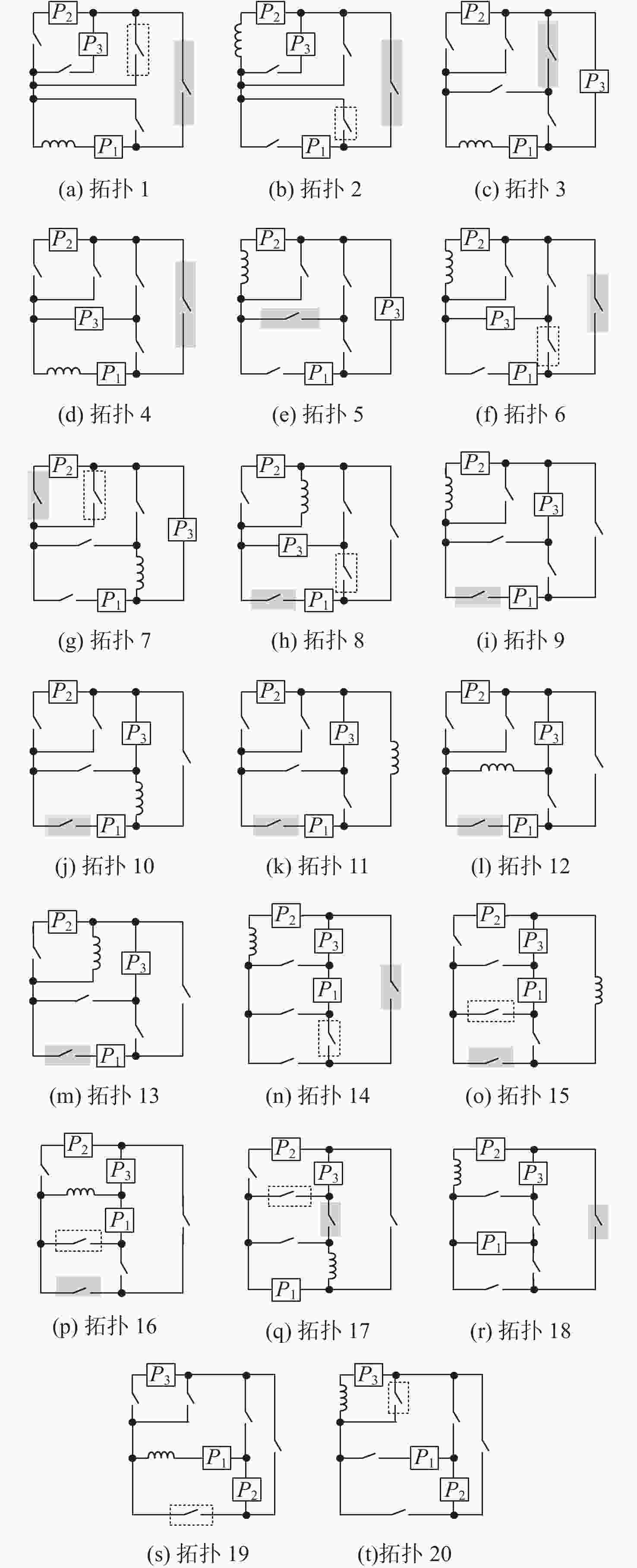

电能变换需求日益增长,推演具有不同性能的新型变换器成为研究热点。当前的推演方法大多未考虑变换器开关冗余的因素,导致推演结果中同时存在含冗余开关的变换器和不含冗余开关的变换器。为从海量的推演结果中快速剔除含冗余开关的变换器,开展了变换器冗余开关自动识别研究。分析变换器冗余开关与其有效开关模态的关系,并在此基础上归纳冗余开关的识别准则;基于图论将识别准则转化为对应的图准则;应用图搜索算法结合图准则建立冗余开关自动识别方法。为验证冗余开关自动识别方法的可行性,将其用于识别现存单电感多端口变换器的冗余开关,识别结果表明:所提方法可以批量、准确地识别出变换器的所有冗余开关,验证了方法的可行性。

Abstract:Up to now, massive power electronics converters have been derived to satisfy various demands in practical applications. However, most of these methods focus on discovering effective converters, ignoring the redundant switches in converters. This paper aims to delete converters with redundant switches efficiently. First, the identification principle is introduced based on the connection between legitimate switching modes and redundant switches. After that, the principle is transformed into the corresponding graph principle. Finally, graph theory and graph searching algorithms are used to develop the auto identification method based on the graph principle. The results demonstrate that all redundant switches may be effectively recognized with the use of computers when the suggested method is applied to single-inductor multi-port converters.

-

Key words:

- graph theory /

- converters /

- redundant switches /

- auto identification /

- switching modes

-

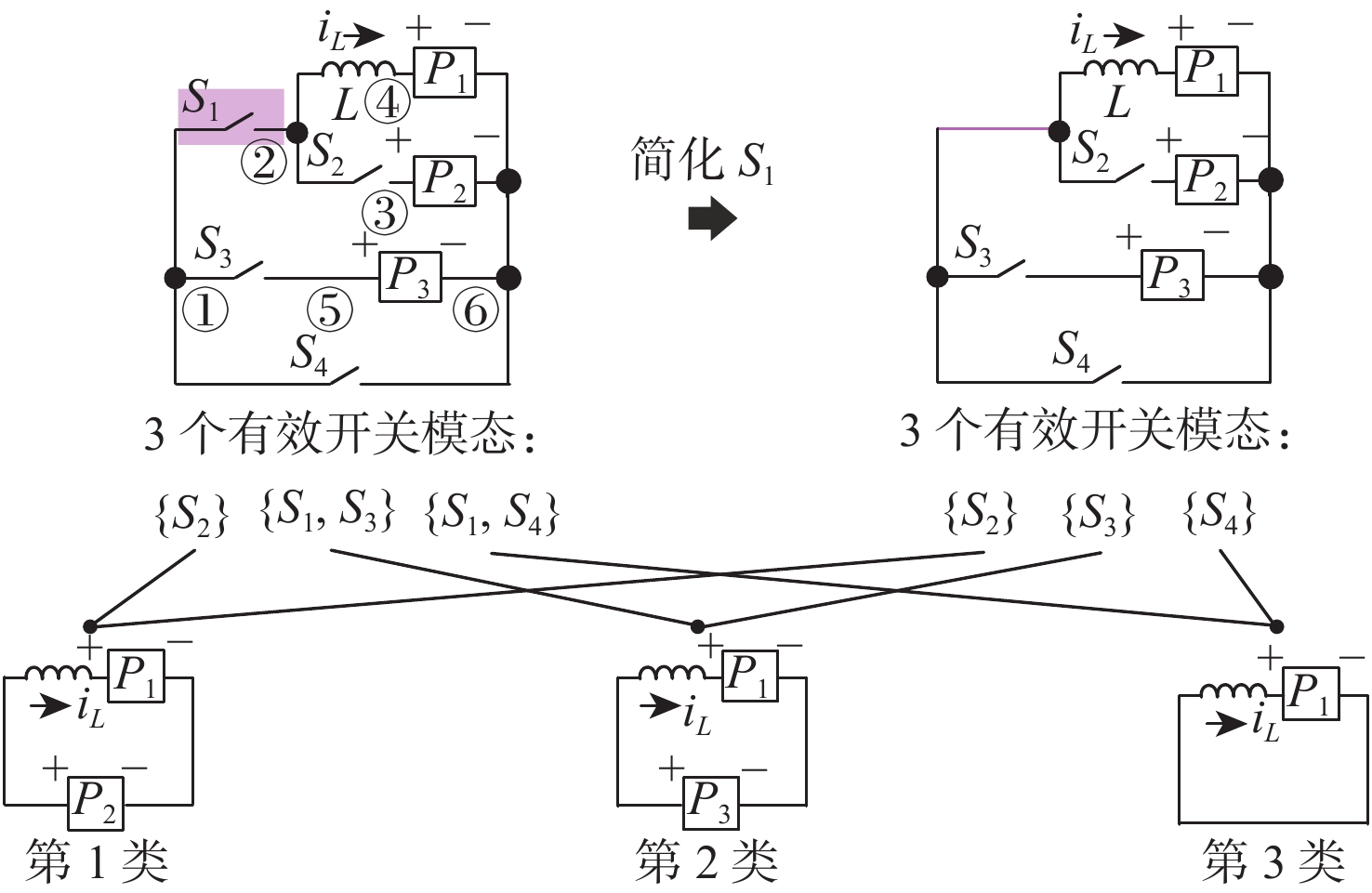

表 1 图1变换器的导通冗余开关识别结果

Table 1. Identification results of turn-on redundant switch for converter in Fig. 1

变化器简图 有效开关

模态回路集与识别结果

原变换器vsm1={S2}

vsm2={S1, S3}

vsm3={S1, S4}$ \begin{gathered} {{{P}}_{{\mathrm{VSM}}}} = \left\{ {p_{{\mathrm{vsm}}1}} = (L,{P_{1 {\text{-}} {\rm{pn}}}},{P_{2 {\text{-}} {\rm{np}}}}),\right. \\ \qquad{p_{{\mathrm{vsm}}2}} = (L,{P_{1 {\text{-}} {\rm{pn}}}},{P_{3 {\text{-}} {\rm{np}}}}), {p_{{\mathrm{vsm}}3}} = \\ \qquad \left.(L,{P_{1 {\text{-}} {\rm{pn}}}})\right\} \\ \end{gathered} $

简化S1vsm1={S2}

vsm2={S3}

vsm3={S4}$\begin{gathered} {{{P}}_{{\mathrm{VSM}} {\text{-}} {{S}}_1 {\text{-}} {\mathrm{on}}}} = \left\{ {p_{{\rm{vsm}}1}} = (L,{P_{1 {\text{-}} {\rm{pn}}}},{P_{2 {\text{-}} {\rm{np}}}}),\right. \\ \qquad {p_{{\rm{vsm}}2}} = (L,{P_{1 {\text{-}} {\rm{pn}}}},{P_{3 {\text{-}} {\rm{np}}}}), {p_{{\rm{vsm}}3}} = \\ \qquad \left. (L,{P_{1 {\text{-}} {\rm{pn}}}}) \right\} \\ \end{gathered}$

PVMS=${{{P}}_{{\mathrm{VSM}} {\text{-}} {{S}}_1 {\text{-}} {\mathrm{on}}}} $,S1导通冗余

简化S2vsm1={S1}

vsm2={S3}

vsm3={S4}$\begin{gathered} {{{P}}_{{\mathrm{VSM}} {\text{-}} {{S}}_2 {\text{-}} {\mathrm{on}}}} = \left\{ {p_{{\rm{vsm}}1}} = (L,{P_{1 {\text{-}} {\rm{pn}}}},{P_{2 {\text{-}} {\rm{np}}}}), \right. \\ \qquad {p_{{\rm{vsm}}2}} = (L,{P_{1 {\text{-}} {\rm{pn}}}},{P_{2 {\text{-}} {\rm{np}}}}), {p_{{\rm{vsm}}3}} = \\ \qquad \left. (L,{P_{1 {\text{-}} {\rm{pn}}}},{P_{2 {\text{-}} {\rm{np}}}}) \right\} \\ \end{gathered} $

PVMS≠${{{P}}_{{\mathrm{VSM}} {\text{-}} {{S}}_2 {\text{-}} {\mathrm{on}}}} $,S2不是导通冗余

简化S3vsm1={S1}

vsm2={S2}$\begin{gathered} {{{P}}_{{\mathrm{VSM}} {\text{-}} {{S}}_3 {\text{-}} {\mathrm{on}}}} = \left\{ {p_{{\rm{vsm}}1}} = (L,{P_{1 {\text{-}} {\rm{pn}}}},{P_{3 {\text{-}} {\rm{np}}}}), \right. \\ \left.{p_{{\rm{vsm}}2}} = (L,{P_{1 {\text{-}} {\rm{pn}}}},{P_{2 {\text{-}} {\rm{np}}}}) \right\} \end{gathered} $

PVSM≠${{{P}}_{{\mathrm{VSM}} {\text{-}} {{S}}_3 {\text{-}} {\mathrm{on}}}} $,S3不是导通冗余

简化S4vsm1={S1}

vsm2={S2}$ \begin{gathered} {{{P}}_{{\mathrm{VSM}} {\text{-}} {{S}}_4 {\text{-}} {\mathrm{on}}}} = \left\{ {p_{{\rm{vsm}}1}} = (L,{P_{1 {\text{-}} {\rm{pn}}}}),\right. \\ \left.{p_{{\rm{vsm}}2}} = (L,{P_{1 {\text{-}} {\rm{pn}}}},{P_{2 {\text{-}} {\rm{np}}}}) \right\} \end{gathered} $

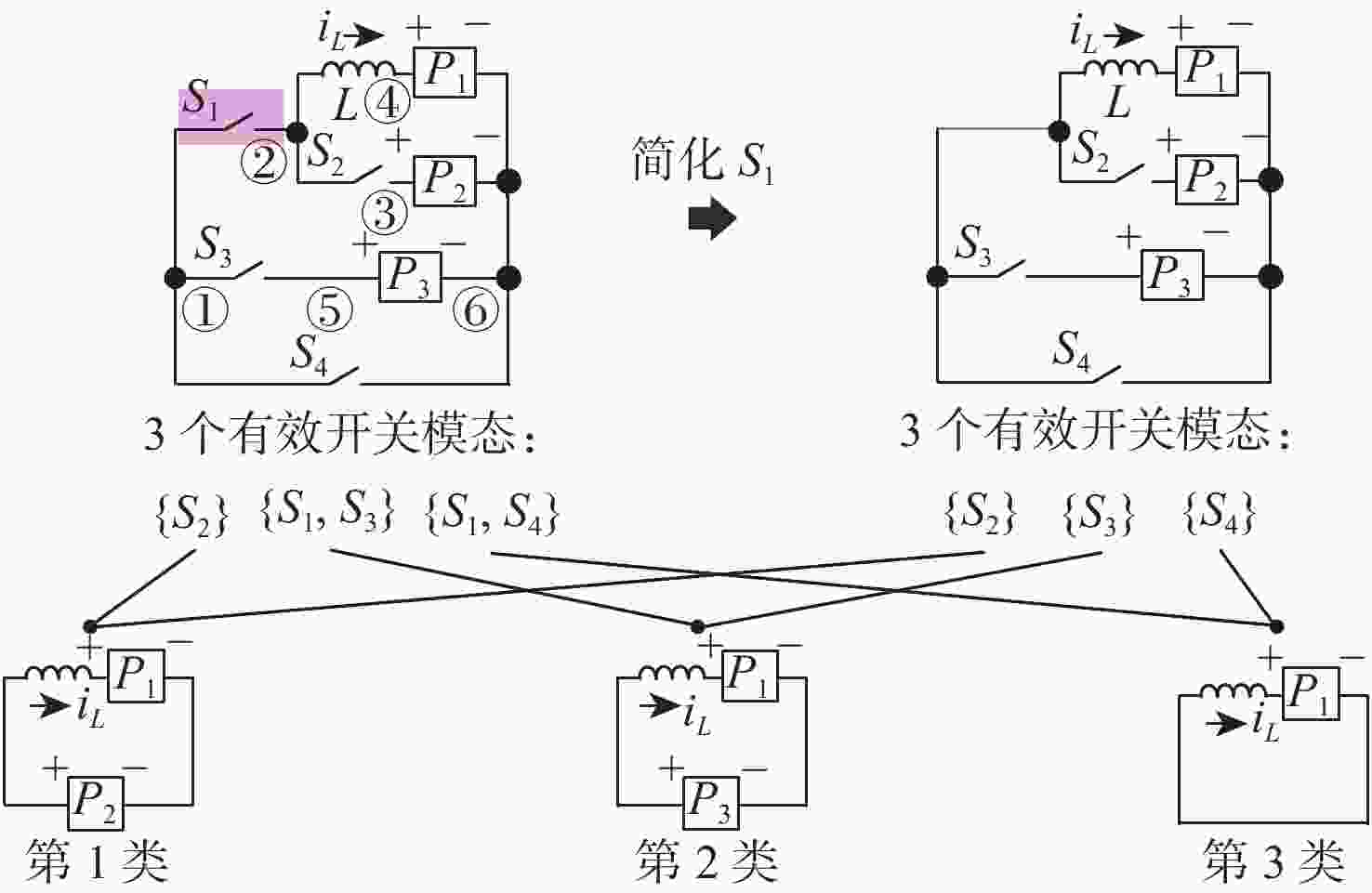

PVMS≠${{{P}}_{{\mathrm{VSM}} {\text{-}} {{S}}_4 {\text{-}} {\mathrm{on}}}} $,S4不是导通冗余表 2 图2变换器的关断冗余开关识别结果

Table 2. Identification results of turn-off redundant switch for converter in Fig. 2

变化器简图 有效开关

模态回路集与识别结果

原变换器vsm1={S1}

vsm2={S2, S3}

vsm3={S2, S5}

vsm4={S3, S4}$ \begin{gathered} {{{P}}}_{{\mathrm{VSM}}}= \left\{{p}_{{\rm{vsm}}1}=(L,{P}_{3{\text{-}} {\rm{pn}}}),\right. \\ \qquad {p}_{{\rm{vsm}}2}=(L,{P}_{3{\text{-}} {\rm{pn}}},{P}_{1{\text{-}} {\rm{np}}}), \\ \qquad {p}_{{\rm{vsm}}3}=(L,{P}_{3{\text{-}} {\rm{pn}}},{P}_{2{\text{-}} {\rm{pn}}}, {P}_{1{\text{-}} {\rm{np}}}), \\ \qquad \left.{p}_{{\rm{vsm}}4}=(L,{P}_{3{\text{-}} {\rm{pn}}},{P}_{2{\text{-}} {\rm{np}}})\right\} \\ \end{gathered} $

删除S1vsm1={S4, S5}

vsm2={S2, S3}

vsm3={S2, S5}

vsm4={S3, S4}$ \begin{gathered} {{{P}}}_{{\mathrm{VSM}}{\text{-}}{{S}}_1{\text{-}}{\mathrm{off}}}= \left\{{p}_{{\rm{vsm}}1}=(L,{P}_{3{\text{-}} {\rm{pn}}}),\right. \\ \qquad {p}_{{\rm{vsm}}2}=(L,{P}_{3{\text{-}} {\rm{pn}}},{P}_{1{\text{-}} {\rm{np}}}), \\ \qquad {p}_{{\rm{vsm}}3}=(L,{P}_{3{\text{-}} {\rm{pn}}},{P}_{2{\text{-}} {\rm{pn}}}, {P}_{1{\text{-}} {\rm{np}}}), \\ \qquad \left.{p}_{{\rm{vsm}}4}=(L,{P}_{3{\text{-}} {\rm{pn}}},{P}_{2{\text{-}} {\rm{np}}})\right\} \\ \end{gathered} $

PVSM=${{{P}}}_{{\mathrm{VSM}}{\text{-}}{{S}}_1{\text{-}}{\mathrm{off}}} $,S1关断冗余

删除S2vsm1={S1}

vsm2={S3, S4}$ \begin{gathered} {{{P}}_{{\mathrm{VSM}} {\text{-}} {{S}}_2 {\text{-}} {\mathrm{off}}}} = \left\{ {p_{{\rm{vsm}}1}} = (L,{P_{3 {\text{-}} {\rm{pn}}}}),\right. \\ \qquad \left.{p_{{\rm{vsm}}2}} = (L,{P_{3 {\text{-}} {\rm{pn}}}},{P_{2 {\text{-}} {\rm{np}}}}) \right\} \\ \end{gathered} $

PVSM≠$ {{{P}}_{{\mathrm{VSM}} {\text{-}} {{S}}_2 {\text{-}} {\mathrm{off}}}} $,S2不是关断冗余

删除S3vsm1={S1}

vsm2={S2, S5}$ \begin{gathered} {{{P}}}_{{\mathrm{VSM}}{\text{-}}{{S}}_3{\text{-}}{\mathrm{off}}}= \left\{{p}_{{\rm{vsm}}1}=(L,{P}_{3{\text{-}} {\rm{pn}}}),\right. \\ \qquad \left.{p}_{{\rm{vsm}}2}=(L,{P}_{3{\text{-}} {\rm{pn}}},{P}_{2{\text{-}} {\rm{pn}}}, {P}_{1{\text{-}} {\rm{np}}})\right\} \\ \end{gathered} $

PVSM≠${{{P}}}_{{\mathrm{VSM}}{\text{-}}{{S}}_3{\text{-}}{\mathrm{off}}} $,S3不是关断冗余

删除S4vsm1={S1}

vsm2={S2, S3}

vsm3={S2, S5}$ \begin{gathered}{{{P}}}_{{\mathrm{VSM}}{\text{-}}{{S}}_4{\text{-}}{\mathrm{off}}}= \left\{{p}_{{\rm{vsm}}1}=(L,{P}_{3{\text{-}} {\rm{pn}}}),\right. \\ \qquad {p}_{{\rm{vsm}}2}=(L,{P}_{3{\text{-}} {\rm{pn}}},{P}_{1{\text{-}} {\rm{np}}}), \\ \qquad \left.{p}_{{\rm{vsm}}3}=(L,{P}_{3{\text{-}} {\rm{pn}}},{P}_{2{\text{-}} {\rm{pn}}},\right. \\ \qquad \left. {P}_{1{\text{-}} {\rm{np}}})\right\} \\ \end{gathered} $

PVSM≠${{{P}}}_{{\mathrm{VSM}}{\text{-}}{{S}}_4{\text{-}}{\mathrm{off}}} $,S4不是关断冗余

删除S5vsm1={S1}

vsm2={S2, S3}

vsm3={S3, S4}$ \begin{gathered}{{{P}}_{{\mathrm{VSM}} {\text{-}} {{S}}_5 {\text{-}} {\mathrm{off}}}} = \left\{ {p_{{\rm{vsm}}1}} = (L,{P_{3 {\text{-}} {\rm{pn}}}}),\right. \\ \qquad {p_{{\rm{vsm}}2}} = (L,{P_{3 {\text{-}} {\rm{pn}}}},{P_{1 {\text{-}} {\rm{np}}}}), \\ \qquad \left.{p_{{\rm{vsm}}2}} = (L,{P_{3 {\text{-}} {\rm{pn}}}},{P_{2 {\text{-}} {\rm{np}}}}) \right\} \\ \end{gathered} $

PVSM≠${{{P}}_{{\mathrm{VSM}} {\text{-}} {{S}}_5 {\text{-}} {\mathrm{off}}}} $,S5不是关断冗余 -

[1] TANG Z T, YANG Y H, BLAABJERG F. Power electronics: the enabling technology for renewable energy integration[J]. CSEE Journal of Power and Energy Systems, 2022, 8(1): 39-52. [2] EHSANI M, SINGH K V, BANSAL H O, et al. State of the art and trends in electric and hybrid electric vehicles[J]. Proceedings of the IEEE, 2021, 109(6): 967-984. doi: 10.1109/JPROC.2021.3072788 [3] PENG W Y, DU S J. The advances in conversion techniques in triboelectric energy harvesting: a review[J]. IEEE Transactions on Circuits and Systems I: Regular Papers, 2023, 70(7): 3049-3062. doi: 10.1109/TCSI.2023.3261780 [4] KIM J S, YOON J O, CHOI B D. A high-light-load-efficiency low-ripple-voltage PFM buck converter for IoT applications[J]. IEEE Transactions on Power Electronics, 2022, 37(5): 5763-5772. doi: 10.1109/TPEL.2021.3131594 [5] CHENG K W E, YE Y M. Duality approach to the study of switched-inductor power converters and its higher-order variations[J]. IET Power Electronics, 2015, 8(4): 489-496. doi: 10.1049/iet-pel.2014.0689 [6] GNANASAMBANDAM K, RATHORE A K, EDPUGANTI A, et al. Current-fed multilevel converters: an overview of circuit topologies, modulation techniques, and applications[J]. IEEE Transactions on Power Electronics, 2017, 32(5): 3382-3401. doi: 10.1109/TPEL.2016.2585576 [7] 胡雪峰, 王琳, 代国瑞, 等. 单开关高增益Boost-Sepic集成变换器[J]. 中国电机工程学报, 2015, 35(8): 2018-2025.HU X F, WANG L, DAI G R, et al. High step-up Boost-Sepic integrated converters with a single switch[J]. Proceedings of the CSEE, 2015, 35(8): 2018-2025(in Chinese). [8] 荣德生, 孙瑄瑨. 高增益耦合电感组合Buck-Boost-Zeta变换器[J]. 中国电机工程学报, 2020, 40(14): 4590-4601.RONG D S, SUN X J. High gain coupled inductance combination Buck-Boost-Zeta converter[J]. Proceedings of the CSEE, 2020, 40(14): 4590-4601(in Chinese). [9] DE ANDRADE J M, SALVADOR M A, COELHO R F, et al. General method for synthesizing high gain step-up DC-DC converters based on differential connections[J]. IEEE Transactions on Power Electronics, 2020, 35(12): 13239-13254. doi: 10.1109/TPEL.2020.2996501 [10] MO L P, CHEN G P, HUANG J M. From components to converters: a fundamental topology derivation method for single-inductor multi-input multi-output converters based on graph theory[C]// Proceedings of the IEEE International Conference on Power Electronics, Computer Applications. Piscataway: IEEE Press, 2021: 458-463. [11] DONG M, LIANG R J, YANG J, et al. Topology derivation of multiport DC-DC converters based on reinforcement learning[J]. IEEE Transactions on Power Electronics, 2023, 38(4): 5055-5064. doi: 10.1109/TPEL.2023.3235053 [12] HUANG Z Q, ZHOU D H, SHEN Z W, et al. Directed graph-based topology derivation method for single-stage multiport inverters[J]. IEEE Transactions on Power Electronics, 2023, 38(11): 14614-14627. doi: 10.1109/TPEL.2023.3305988 [13] CHEN Y, BAI J B, KANG Y. A nonisolated single-inductor multiport DC-DC topology deduction method based on reinforcement learning[J]. IEEE Journal of Emerging and Selected Topics in Power Electronics, 2022, 10(6): 6572-6585. doi: 10.1109/JESTPE.2021.3128270 [14] LI H, LI Y M, WANG W C, et al. Programmable topology deduction algorithm for S1D2C1L1 type DC-DC converters based on graph theory[C]//Proceedings of the 14th International FLINS Conference. Singapore: World Scientific, 2020. [15] 李虹, 王文财, 李亚敏, 等. 基于图论的S1D1L2C1型DC-DC变换器可编程拓扑搜索算法[J]. 中国电机工程学报, 2021, 41(16): 5670-5683.LI H, WANG W C, LI Y M, et al. Programmable topology searching algorithm for S1D1L2C1 type DC-DC converters based on graph theory[J]. Proceedings of the CSEE, 2021, 41(16): 5670-5683(in Chinese). [16] CHEN G P, JIN Z F, LIU Y W, et al. Programmable topology derivation and analysis of integrated three-port DC-DC converters with reduced switches for low-cost applications[J]. IEEE Transactions on Industrial Electronics, 2019, 66(9): 6649-6660. [17] MO L P, HUANG J M, CHEN G P, et al. Computer-aided systematic topology derivation of single-inductor multi-input multi-output converters from working principle[J]. IEEE Transactions on Circuits and Systems I: Regular Papers, 2022, 69(6): 2637-2649. doi: 10.1109/TCSI.2022.3159718 [18] ERICKSON R W, MAKSIMOVIĆ D. Fundamentals of power electronics[M]. Berlin: Springer, 2001. [19] 张永, 李睿, 年福忠. 算法与数据结构[M]. 北京: 国防工业出版社, 2008.ZHANG Y, LI R, NIAN F Z. Algorithms and data structures[M]. Beijing: National Defense Industry Press, 2008(in Chinese). [20] XIE B Z, QI C, BEN H Q, et al. The applications of graph theory in electric network[C]//Proceedings of the International Conference on Sensing, Diagnostics, Prognostics, and Control. Piscataway: IEEE Press, 2019: 780-784. -

下载:

下载: